| A                                           |                                                                                                                                        | Reg. No. :            |                              |                       |  |  |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------|-----------------------|--|--|--|--|--|--|

|                                             |                                                                                                                                        | Question Pa           | per Code: 53306              |                       |  |  |  |  |  |  |

| B.E. / B.Tech. DEGREE EXAMINATION, NOV 2023 |                                                                                                                                        |                       |                              |                       |  |  |  |  |  |  |

| Third Semester                              |                                                                                                                                        |                       |                              |                       |  |  |  |  |  |  |

| Electrical and Electronics Engineering      |                                                                                                                                        |                       |                              |                       |  |  |  |  |  |  |

| 15UEE306 -DIGITAL LOGIC CIRCUITS            |                                                                                                                                        |                       |                              |                       |  |  |  |  |  |  |

|                                             | (Regulation 2015)                                                                                                                      |                       |                              |                       |  |  |  |  |  |  |

| Dura                                        | ation: Three hours                                                                                                                     | <b>A</b>              |                              | n: 100 Marks          |  |  |  |  |  |  |

| Answer ALL Questions                        |                                                                                                                                        |                       |                              |                       |  |  |  |  |  |  |

|                                             |                                                                                                                                        | PART A - (1           | $0 \ge 1 = 10 \text{ Marks}$ |                       |  |  |  |  |  |  |

| 1.                                          | Convert binary 11111                                                                                                                   | 1110010 to hexade     | ecimal.                      | CO1- R                |  |  |  |  |  |  |

|                                             | (a) EE2 <sub>16</sub>                                                                                                                  | (b) FF2 <sub>16</sub> | (c) 2FE <sub>16</sub>        | (d) FD2 <sub>16</sub> |  |  |  |  |  |  |

| 2.                                          | Any signed negative l                                                                                                                  | CO1- R                |                              |                       |  |  |  |  |  |  |

|                                             | (a) MSB                                                                                                                                | (b) LSB               | (c) Byte                     | (d) Nibble            |  |  |  |  |  |  |

| 3.                                          | Canonical form is a u                                                                                                                  | nique way of repres   | senting                      | CO2- R                |  |  |  |  |  |  |

|                                             | (a) SOP                                                                                                                                | (b) Minterm           | (c) Boolean Expressions      | (d) POS               |  |  |  |  |  |  |

| 4.                                          | The format used to present the logic output for the various combinations of logic inputs to a gate is called                           |                       |                              |                       |  |  |  |  |  |  |

|                                             | (a) Truth table.                                                                                                                       |                       | (b) Input logic function.    |                       |  |  |  |  |  |  |

|                                             | (c) Boolean constant                                                                                                                   |                       | (d) Boolean variable         |                       |  |  |  |  |  |  |

| 5.                                          | What is a shift register that will accept a parallel input, or a CO3- R bidirectional serial load and internal shift features, called? |                       |                              |                       |  |  |  |  |  |  |

|                                             | (a) Tri state                                                                                                                          | (b) End around        | (c) Universal                | (d) Conversion        |  |  |  |  |  |  |

| 6.                                          | A basic S-R flip-flop basic logic gates?                                                                                               | can be constructed    | by cross-coupling of which   | CO3- R                |  |  |  |  |  |  |

|                                             | (a) AND or OR                                                                                                                          | (b) XOR or XNC        | 0R (c) NOR or NAND           | (d) AND or NOR        |  |  |  |  |  |  |

| 7.  | Table that is not a part of asynchronous analysis procedure is                                                                                                       |                                                             |                         |                            |               | CO4- R  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------|----------------------------|---------------|---------|--|--|--|--|

|     | (a) ]                                                                                                                                                                | Fransition table                                            | (b) State table         | (c) Flow table             | (d) Excitatio | n table |  |  |  |  |

| 8.  | How much locations an 8-bit address code can select in memory?                                                                                                       |                                                             |                         |                            |               | CO4- R  |  |  |  |  |

|     | (a) 8                                                                                                                                                                | 8 locations (b) 256 locations (c) 65,536 locations (d) 131, |                         | (d) 131,072                | locations     |         |  |  |  |  |

| 9.  | Eacl                                                                                                                                                                 | h unit to be model                                          |                         | CO5- R                     |               |         |  |  |  |  |

|     | (a) Behavioral model                                                                                                                                                 |                                                             |                         | (b) Design architecture    |               |         |  |  |  |  |

|     | (c) Design entity                                                                                                                                                    |                                                             |                         | (d) Structural model       |               |         |  |  |  |  |

| 10. | <ul><li>Which of the following describes the connections between the entity port and the local component?</li><li>(a) Port map</li><li>(b) One to many map</li></ul> |                                                             |                         |                            |               |         |  |  |  |  |

|     | (c) One to one map (d) Many to                                                                                                                                       |                                                             |                         |                            |               |         |  |  |  |  |

|     | PART - B (5 x 2= 10 Marks)                                                                                                                                           |                                                             |                         |                            |               |         |  |  |  |  |

| 11. | Why Excess-3 code is called self complementing code? CO1- U                                                                                                          |                                                             |                         |                            |               |         |  |  |  |  |

| 12. | . Draw the circuit diagram of full adder using two half adders.                                                                                                      |                                                             |                         |                            |               |         |  |  |  |  |

| 13. | . Compare Moore and Melay circuits.                                                                                                                                  |                                                             |                         |                            |               | CO3- R  |  |  |  |  |

| 14. | . Define static hazard.                                                                                                                                              |                                                             |                         |                            |               | CO4- R  |  |  |  |  |

| 15. | What are the various modeling techniques in VHDL?                                                                                                                    |                                                             |                         |                            |               | CO5- R  |  |  |  |  |

|     |                                                                                                                                                                      |                                                             | PART – C (5             | x 16= 80 Marks)            |               |         |  |  |  |  |

| 16. | (a)                                                                                                                                                                  | (i) Encode the b<br>Hamming Code.                           | pinary word 1011 into   | o seven bit even parity    | CO1- U        | (10)    |  |  |  |  |

|     | (ii) Write short notes on binary weighted code.                                                                                                                      |                                                             |                         | CO1- U                     | (6)           |         |  |  |  |  |

|     |                                                                                                                                                                      |                                                             | Or                      |                            |               |         |  |  |  |  |

|     | (b)                                                                                                                                                                  | (i) With a neat<br>TTL NAND gate                            | -                       | e working of two input     | CO1- U        | (10)    |  |  |  |  |

|     |                                                                                                                                                                      | (ii) Compare tote                                           | em pole and open colle  | ector outputs.             | CO1- U        | (6)     |  |  |  |  |

| 17. | (a)                                                                                                                                                                  | Design a 3:8 dea<br>and maxterm ger                         | -                       | operation as a minterm     | CO2- Ana      | (16)    |  |  |  |  |

|     | (b)                                                                                                                                                                  | Design a circuit<br>equivalent gray c                       | that can convert a four | r bit binary code into its | CO2- Ana      | (16)    |  |  |  |  |

18. (a) Design a MOD-7 synchronous counter using JK flip flop and CO3- Ana (16) implement it. Also draw its timing diagram.

Or

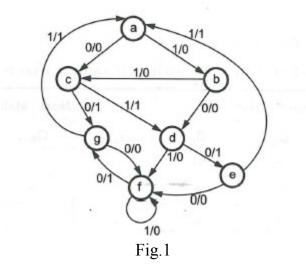

(b) Design a clocked sequential circuit for the state diagram CO3- Ana (16) shown in Fig.1 using T flip flop.

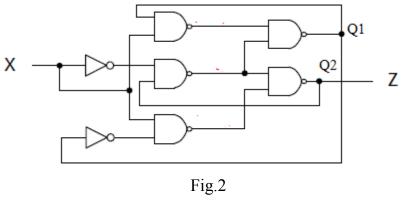

19. (a) (i) Analyze the following asynchronous network shown in CO4-Ana (16) Fig.2 using a flow table. Starting in the total stable state for which X = Z = 0.

(ii) Are there any races in the flow table?

Or

(b) Show how to programme the fusible links to get a 4 bit gray CO4-Ana (16) code from the binary inputs using PLA and PAL and compare the design requirements with PROM.

20. (a) Write a VHDL program for full adder using structural CO5-U (16) modeling and 1: 4 DMUX using data flow modeling.

## Or

| (b) (i) | Explain the various operators supported by VHDL.                     | CO5-U | (8) |

|---------|----------------------------------------------------------------------|-------|-----|

|         | Write a VHDL code to realize a decade counter with avioral modeling. | CO5-U | (8) |