Question Paper Code: 51446

## B.E. /B. Tech. DEGREE EXAMINATION, MAY/JUNE 2016

## **Third Semester**

# Electronics and Communication Engineering EC 2205/EC 36/080290011 – ELECTRONIC CIRCUITS – I

(Common to Medical Electronics Engineering)

(Regulations 2008)

Time: Three Hours

Maximum: 100 Marks

Answer ALL questions.  $PART - A (10 \times 2 = 20 Marks)$

- 1. List out the advantages of self bias over other BJT biasing methods.

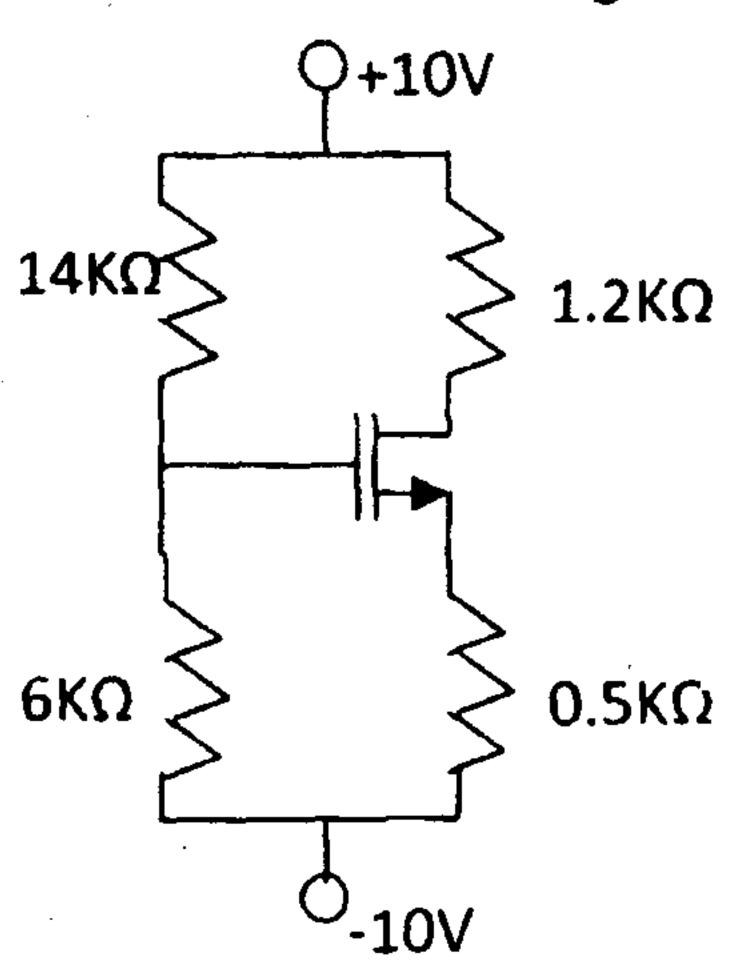

- 2. Draw the DC load line of the circuit shown in Figure-2.

Figure-2

- 3. Define Miller's theorem.

- 4. Define CMRR. How to improve CMRR?

- 5. Differentiate between Class A and Class S amplifier.

- 6. Define cross-over distortion. How to overcome cross-over distortion?

- 7. Determine  $f_{3B}$  of the short-circuit current gain of BJT, rbe = 2.6k $\Omega$ , Cbe = 2pF and Cb c= 0.1pF

- 8. Differentiate between half-wave-rectifier and full-wave-rectifier.

- 9. Define gain-bandwidth product.

- 10. Compare between LC and  $\pi$  filter.

51446

11. (a) (i) Determine the quiescent current and voltage values in a p-channel JFET circuit. (6)

Figure – 11(a) (i)

(ii) For the MOSFET transistor in the circuit in Figure 11(a) (ii), the parameters are  $V_{th} = 2V$ ,  $kn' = 60\mu A/V^2$  and W/L=60. (1) Determine  $V_{th} = V_{th} = V_{th}$

Figure – 11(a) (ii) OR

- (b) (i) Derive an expression for the stability factor of a self-bias circuit.

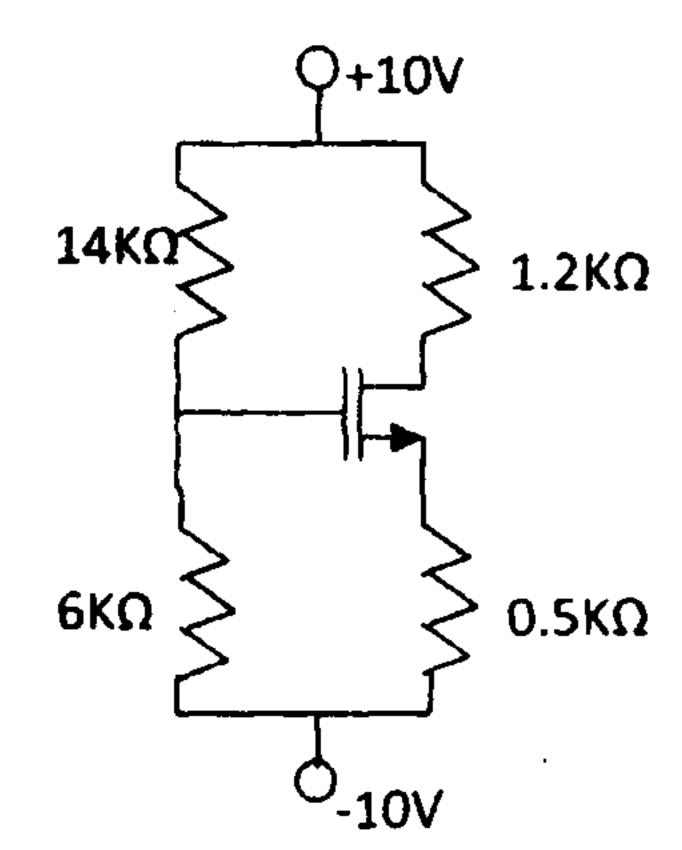

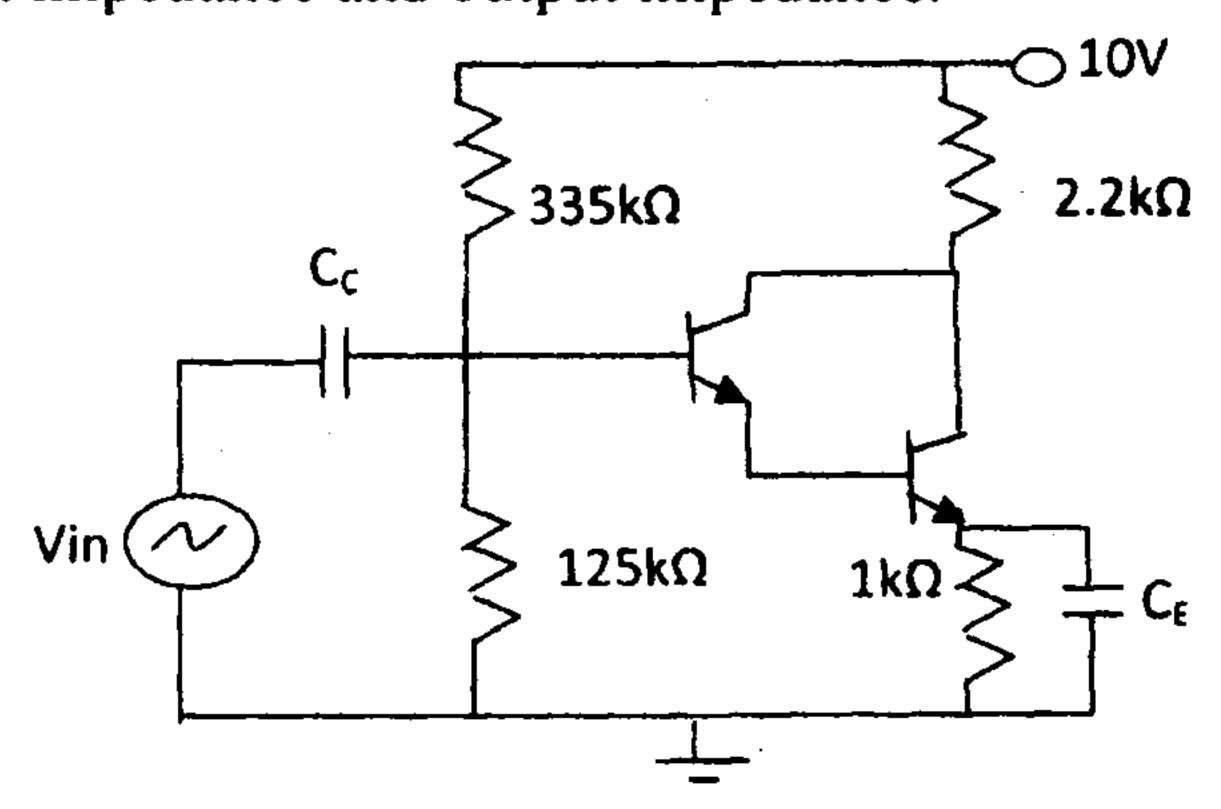

- (ii) The circuit in Figure 11(b) (ii), let  $\beta = 100$  (1) Find  $V_{TH}$  and  $R_{TH}$  for the base circuit (2) Determine  $I_{CQ}$  and  $V_{CEQ}$  (3) Draw the DC load line. (10)

Figure 11(b) (ii)

**(6)**

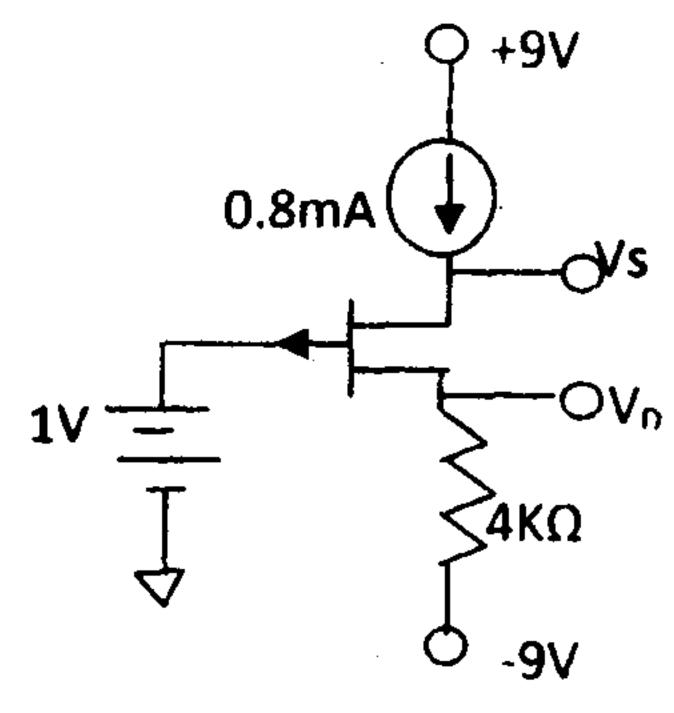

12. (a) (i) For each transistor in the Darlington circuit shown in Figure 12(a) (i) has the parameters of  $\beta = 100$ ,  $V_A = \infty$ . Determine its overall voltage gain, input impedance and output impedance.

Figure – 12(a) (i)

- (ii) Determine the small signal voltage gain, input impedance and output impedance of common source FET amplifier.

OR

(8)

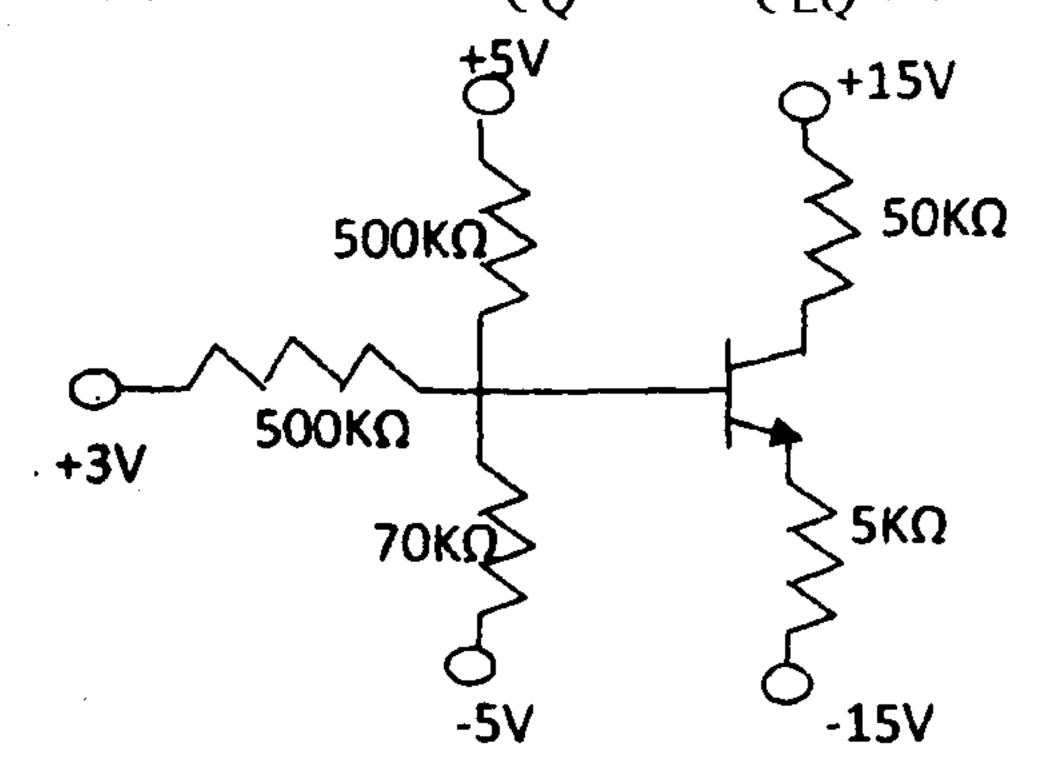

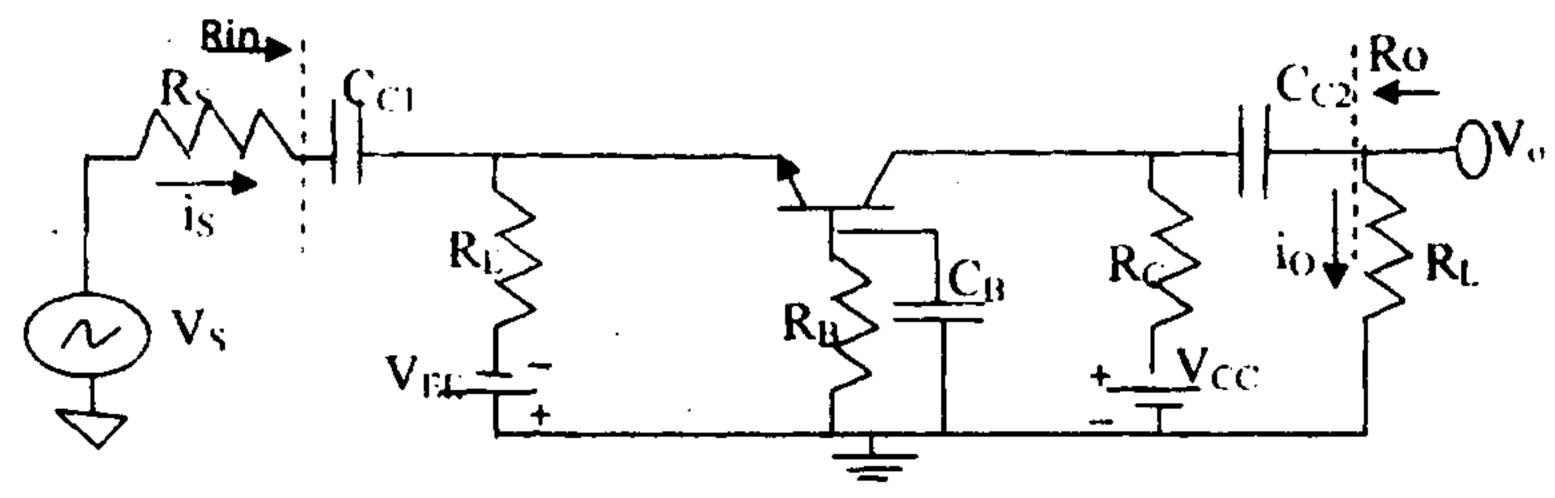

- (b) For the circuit in Figure 12(b), the parameters are  $R_B = 100 \text{ k}\Omega$ ,  $R_E = 10 \text{ k}\Omega$ ,  $R_C = 10 \text{ k}\Omega$ ,  $V_{CC} = V_{EE} = 10 \text{ V}$ ,  $R_L = 1 \text{ k}\Omega$ ,  $R_S = 1 \text{ k}\Omega$ ,  $R_S = 125 \text{ and } V_A = \infty$ . (1) Determine the small signal voltage gain (2) Determine small signal current gain (3) Determine the input resistance, fin (4) Determine the output resistance,  $R_o$ .

**Figure – 12(b)**

- 13. (a) (i) Discuss the frequency response of multistage amplifier in detail. (8)

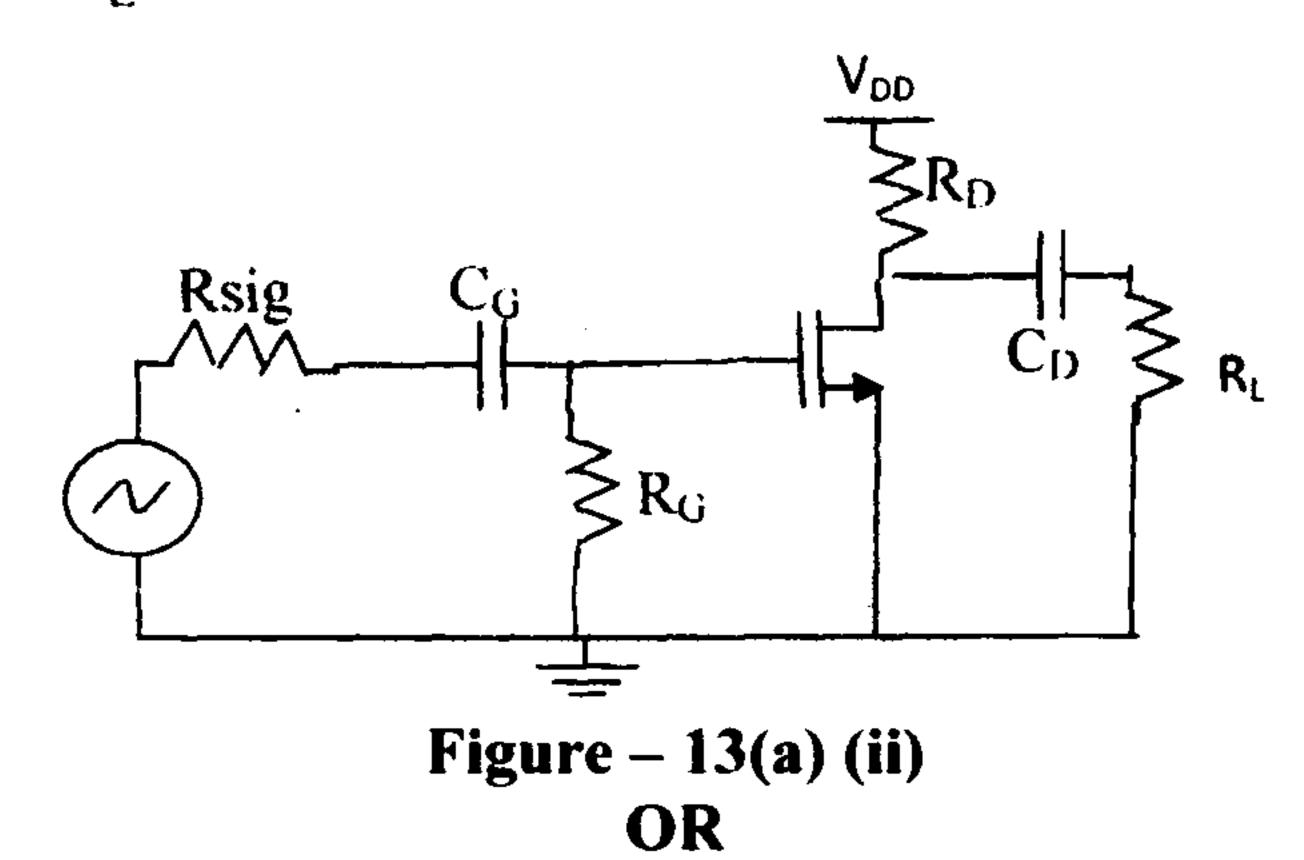

- (ii) Determine the midband gain, upper Cutoff frequency of a Common-Source amplifier fed with the signal having internal resistance Rsig =  $100 \text{ k}\Omega$  (vide Figure 13(a) (ii)). The amplifier has  $R_G = 4.7 \text{ M}\Omega$ ,  $R_D = R_I = 15 \text{ k}\Omega$ , gm = 1 m A/V, ro =  $150\Omega$ , Cgs = 1 pF and Cgd = 0.4 pF. (8)

**(8)**

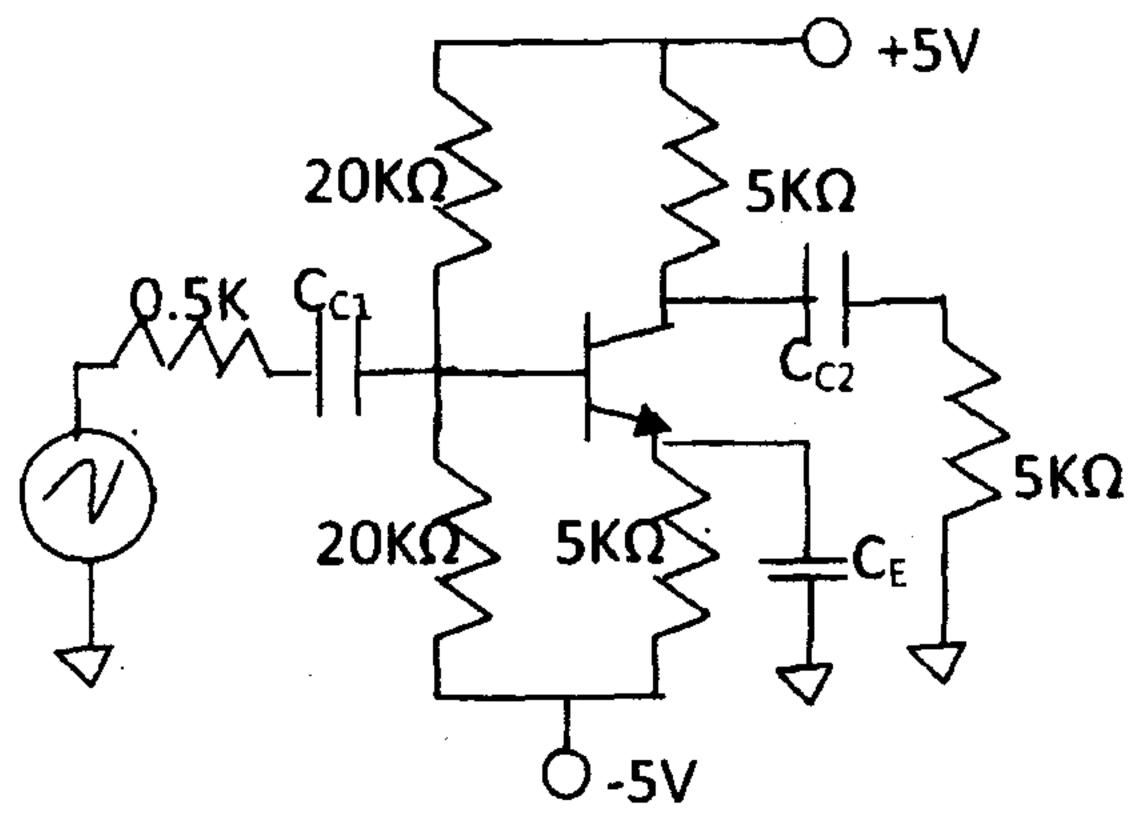

(b) Determine the mid-band gain and bandwidth of a CE amplifier (vide Figure 13(b)). Assume lower cutoff frequency is 100 Hz, (ii) Find  $C_{C1}$ ,  $C_{C2}$  and  $C_{E}$ . Let  $\beta = 100$ , cbe = 4pF, cbc=0.2pF and  $V_A = \infty$ . (16)

**Figure** – **13(b)**

- 14. (a) (i) Explain the second-order harmonic distortion in detail. (8)

- (ii) Explain the Class D amplifier in detail. (8)

#### OR

- (b) (i) Briefly discuss the complementary symmetry (Class-B) push-pull amplifier. (8)

- (ii) Discuss the thermal stability and heat sinks in detail. (8)

- 15. (a) Explain the Switched-Mode power supply design in detail. (16)

### OR

- (b) (i) Explain the AC power control using SCR in detail. (8)

- (ii) Explain the performances measures of rectifiers in detail. (8)