| Reg. No.: |  |  |  |  |  |

|-----------|--|--|--|--|--|

**Question Paper Code: 51336**

## B.E. / B.Tech. DEGREE EXAMINATION, NOV 2016

## Third Semester

## Electrical and Electronics Engineering

## 15UEE306 - DIGITAL LOGIC CIRCUITS

(Regulation 2015)

Duration: Three hours Maximum: 100 Marks

|    |                                                                                                 | Answer ALL Q        | uestions                                                                     |                       |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------|-----------------------|--|--|--|--|

|    | PART A - $(10 \times 1 = 10 \text{ Marks})$                                                     |                     |                                                                              |                       |  |  |  |  |

| 1. | In standard TTL the 'totem pole' stage refers to the                                            |                     |                                                                              |                       |  |  |  |  |

|    | <ul><li>(a) multi-emitter input s</li><li>(c) output buffer</li></ul>                           | `                   | <ul><li>(b) phase splitter</li><li>(d) open collector output stage</li></ul> |                       |  |  |  |  |

| 2. | What is the gray code for 10                                                                    | 000?                |                                                                              |                       |  |  |  |  |

|    | (a) 1010                                                                                        | (b) 1000            | (c) 1011                                                                     | (d) 1100              |  |  |  |  |

| 3. | 3. The digital multiplexer is basically a combination logic circuit to perform the operation of |                     |                                                                              |                       |  |  |  |  |

|    | (a) AND-AND                                                                                     | (b) OR-OR           | (c) AND-OR                                                                   | (d) OR-AND            |  |  |  |  |

| 4. | A combinational circuit that                                                                    | performs the addi   | tion of two bits is calle                                                    | d                     |  |  |  |  |

|    | (a) Full adder                                                                                  | (b) Full subtractor | r (c) Half subtractor                                                        | (d) Half adder        |  |  |  |  |

| 5. | The output $Q_n$ of a J-K flip<br>The input $J_n$ and $K_n$ are resp                            | •                   | ange to one when a clo                                                       | ock pulse is applied. |  |  |  |  |

(b) 0 and *X*

(a) 1 and *X*

(c) *X* and 0

(d) *X* and 1

| 6.  | A flip-                                                                             | flop output transition                    | serves as clock to ne        | ext flip-flop is called                                                                |                           |  |  |

|-----|-------------------------------------------------------------------------------------|-------------------------------------------|------------------------------|----------------------------------------------------------------------------------------|---------------------------|--|--|

|     | <ul><li>(a) ripple counter</li><li>(c) shift register</li></ul>                     |                                           |                              | <ul><li>(b) parallel counter</li><li>(d) none of the above</li></ul>                   |                           |  |  |

| 7.  | An un                                                                               | wanted switching tran                     | asients occurs at the o      | output of a circuit are                                                                |                           |  |  |

|     | (a)                                                                                 | ) races                                   | (b) cycles                   | (c) hazards                                                                            | (d) harmonics             |  |  |

| 8.  | A PLA                                                                               | A can be used                             |                              |                                                                                        |                           |  |  |

|     | <ul><li>(a) as a microprocessor</li><li>(c) to realize a sequential logic</li></ul> |                                           |                              | <ul><li>(b) as a dynamic memory</li><li>(d) to realize a combinational logic</li></ul> |                           |  |  |

| 9.  | Which                                                                               | one is unary operator                     | r in VHDL?                   |                                                                                        |                           |  |  |

|     | (a)                                                                                 | ) +(sign)                                 | (b) not                      | (c) mod                                                                                | (d) rol                   |  |  |

| 10. | Which                                                                               | is used to verify the                     | design function?             |                                                                                        |                           |  |  |

|     | (a)                                                                                 | ) packages                                | (b) libraries                | (c) test bench                                                                         | (d) subprogram            |  |  |

|     |                                                                                     |                                           | PART - B (5 x $2 = 10$       | 0 Marks)                                                                               |                           |  |  |

| 11. | Define                                                                              | e fan-in and fan-out.                     |                              |                                                                                        |                           |  |  |

| 12. | Give the                                                                            | he application of dem                     | ultiplexer.                  |                                                                                        |                           |  |  |

| 13. | Disting                                                                             | guish between sync                        | hronous sequential           | circuits and async                                                                     | hronous sequential        |  |  |

| 14. | Define                                                                              | e race in asynchronous                    | s sequential circuit.        |                                                                                        |                           |  |  |

| 15. | What i                                                                              | is test bench in VHDI                     | ٠.                           |                                                                                        |                           |  |  |

|     |                                                                                     | I                                         | $PART - C (5 \times 16 = 8)$ | 30 Marks)                                                                              |                           |  |  |

| 16. | (a) (i)                                                                             | Write a brief notes                       | about error detection        | and correction codes                                                                   | . (8)                     |  |  |

|     | (ii                                                                                 | ) Explain the operation                   | on and characteristics       | s of DTL circuit.                                                                      | (8)                       |  |  |

|     |                                                                                     |                                           | Or                           |                                                                                        |                           |  |  |

|     | (b) (i)                                                                             | Explain the operation with Tottem pole or |                              | circuit diagram for 2                                                                  | 2 input NAND gate<br>(12) |  |  |

|     | (ii                                                                                 | ) Write short notes or                    | •                            |                                                                                        | (4)                       |  |  |

17. (a) Reduce the following using K-map

(i)

$$F(w, x, y, z) = \sum m(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$$

(4)

(ii)

$$g(w, x, y, z) = \sum m(1, 3, 4, 6, 11) + \sum d(0, 8, 10, 12, 13)$$

(4)

(iii)

$$Y = (A, B, C, D) = \prod M(0, 2, 8, 9, 12, 13, 15)$$

(4)

(iv)

$$Y = (A, B, C, D) = \prod M(1, 2, 3, 8, 9, 10, 11, 14) + d(7, 15).$$

(4)

Or

- (b) (i) Implement Excess 3 to BCD code converter circuit. (8)

- (ii) Implement the given boolean function using 4:1 Multiplexer,

$$F(A, B, C, D) = \sum m(0, 1, 2, 4, 6, 9, 12, 14). \tag{8}$$

- 18. (a) (i) Design a 4-bit synchronous up-counter using JK flip flop. (8)

- (ii) Using D-flip flop, design a synchronous counter which counts in the sequence 000, 001, 010, 011, 100, 101, 110, 111, 000. (8)

Or

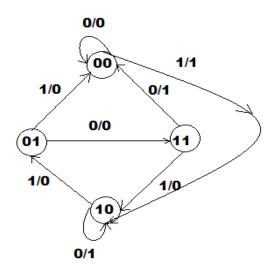

(b) Design a sequential circuit with JK flip-flop.

19. (a) Discuss the different types of hazards that occurs in asynchronous sequential circuits and combinational circuits. (16)

Or

(b) Explain with a suitable example the procedure for analyzing synchronous sequential circuit. (16)

(16)

| 20. | (a) | (i)  | Write a VHDL code for a full adder.                                  | (8) |

|-----|-----|------|----------------------------------------------------------------------|-----|

|     |     | (ii) | Explain the operation of RTL data path design with suitable diagram. | (8) |

|     |     |      | Or                                                                   |     |

|     | (b) | Wr   | te a VHDL code for SR flip flop and D flip flop.                     | (16 |

|     |     |      |                                                                      |     |