|           | 1 1 |  |  |  |  |

|-----------|-----|--|--|--|--|

| Reg. No.: |     |  |  |  |  |

## Question Paper Code: 65033

5 Year M.Sc. DEGREE EXAMINATION, MAY/JUNE 2013.

First Semester

Software Engineering

XCS 114/10677 SW 104 — DIGITAL PRINCIPLES

(Common to 5 Year M.Sc. Information Technology and 5 Year M.Sc. Computer Technology)

(Regulation 2003/2010)

Time: Three hours

Maximum: 100 marks

Answer ALL questions.

PART A —  $(10 \times 2 = 20 \text{ marks})$

- 1. Convert the decimal numbers 68 and 0.4375 to binary numbers.

- 2. Simplify the following Boolean expression to minimum number of literals. Y = ABC + A'B + ABC'

- 3. Simplify the following Boolean functions using three variable maps.  $F(A,B,C) = \Sigma(0,2,6,7)\,.$

- 4. Draw the logic diagram of a 2 to 4 decoder including an enable input using NOR gates.

- 5. Construct a J-K flip-flop using D-flip-flop.

- 6. Write HDL behavioural description of D-flip-flop with asynchronous reset.

- 7. What are the general capabilities of the shift register?

- 8. What are the difference between ring counter and Johnson counter?

- 9. Draw the logic circuit and truth table of S-R latch using NAND gates.

- 10. What is Hazard in combinational circuit? Explain with an example

## PART B — $(5 \times 16 = 80 \text{ marks})$

| 11. | (a) | (i)   | Perform the following binary division in binary.                                                                                                   | (4)                                      |  |  |

|-----|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|

|     |     |       | 1011111 ÷ 101                                                                                                                                      |                                          |  |  |

|     | /   | (ii)  | Add and multiply the hexadecimal numbers 2E and 34 withou converting to decimal.                                                                   |                                          |  |  |

|     |     | (iii) | Represent the decimal numbers 6027 and 4256 in BCD, excess code and 2421 code.                                                                     |                                          |  |  |

|     |     |       | Or                                                                                                                                                 |                                          |  |  |

|     | (b) | (i)   | The Boolean function $F = xy'z + x'y'z + w'xy + wx'y + wxy$ .                                                                                      | (8)                                      |  |  |

|     |     |       | Simplify the function to a minimum number of literals and obtathe truth table.                                                                     | iin                                      |  |  |

|     |     |       | Draw the logic diagram for the simplified expression.                                                                                              | (6) (8) (8) (10) (6) Use and (6) (6) (6) |  |  |

|     |     | (ii)  | Convert the following expression into sum of products and product of sum.                                                                          |                                          |  |  |

|     |     |       | Y = x' + x(x + y')(y + z').                                                                                                                        |                                          |  |  |

| 12. | (a) | (i)   | Simplify the following Boolean function using five variable map.(1                                                                                 | 10)                                      |  |  |

|     |     |       | F (A, B, C, D, E) = (0, 2, 4, 6, 9, 13, 21, 23, 25, 29, 31)                                                                                        |                                          |  |  |

|     |     | (ii)  | Write the HDL description of the circuit for the following Booles function.                                                                        |                                          |  |  |

|     |     |       | x = A(CD + B) + BC'                                                                                                                                |                                          |  |  |

|     |     |       | Or                                                                                                                                                 |                                          |  |  |

|     | (b) | (i)   | Design a binary multiplier that multiplies two 4-bit numbers. U<br>AND gates and binary adders. (1                                                 |                                          |  |  |

|     |     | (ii)  | Implement the following Boolean function with a multiplexer. $F(x,y,z) = \Sigma(1,2,6,7)$                                                          | (6)                                      |  |  |

| 13. | (a) |       | quential circuit with two D-flip-flops A and B, two inputs $x$ and $y$ are output $z$ is specified by the following next-state and output equation |                                          |  |  |

|     |     | A(t + | A(t+1) = x'y + xA                                                                                                                                  |                                          |  |  |

|     |     | B(t + | -1) = x'B + xA                                                                                                                                     |                                          |  |  |

|     |     |       |                                                                                                                                                    |                                          |  |  |

|     |     | (i)   | List the state table for the sequential circuit.                                                                                                   | (6)                                      |  |  |

|     |     | (ii)  | Draw the corresponding state diagram.                                                                                                              | (6)                                      |  |  |

|     |     | (iii) | Draw the logic diagram of the circuit.                                                                                                             | (4)                                      |  |  |

|     |     |       | $\operatorname{Or}$                                                                                                                                |                                          |  |  |

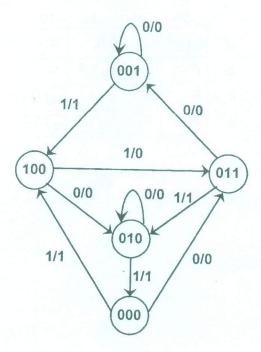

(b) A sequential circuit has three flip-flops A, B, C, one input x and one output y. The state diagram is given in Figure-1. The circuit is to be designed by treating the unused states as don't care conditions using J-K flip-flops. (16)

Figure 1

- 14. (a) (i) Design a serial adder using shift register. (8)

- (ii) Design a three bit BCD ripple counter using J-K flip-flops. (8)

Or

- (b) (i) Design a counter with the following repeated binary sequences using D-flip-flops. (8) y=(0,1,2,4,6)

- (ii) Write HDL behavioural and structural description of ripple counter. (8)

- 15. (a) An asynchronous sequential circuit has two internal states and one output. The excitation and output function describing the circuit are.

$$Y_1 = x_1 x_2 + x_1 y_2' + x_2' y_1$$

$$Y_2 = x_2 + x_1 y_1' y_2 + x_1' y_1$$

$z = x_2 + y_1$

- (i) Derive the transition table and output map.

- (6)

(ii) Obtain the flow table for the circuit.

(6)

(iii) Draw the logic diagram of the circuit.

(4)

Or

(b) (i) Obtain a binary state assignment for the reduced flow table shown in Figure 2. Avoid critical race conditions. (8)

|   | $X_1X_2$ |      |      |      |  |  |

|---|----------|------|------|------|--|--|

|   | 00       | 01   | 11   | 10   |  |  |

| а | a,0      | 3,1  | b, - | d, - |  |  |

| b | а,-      | ь,0  | Ь,0  | C, - |  |  |

| С | a,-      | -, - | d,-  | c,0  |  |  |

| d | a,-      | а,-  | d,1  | a,1  |  |  |

Figure 2

(ii) Obtain the logic diagram of the circuit using NAND latches and gates. (8)